一、研究背景

通过晶体管表面电势的有效调制,负电容引起低于基本极限的阈值摆幅(SS)。尽管多晶Pb(Zr0.2Ti0.8)O3和HfZrO2薄膜在几微秒内发生了负迁移,但代替传统电介质使用时,低SS在大范围的漏极电流是不持久的。

二、研究成果

鉴于此,韩国成均馆大学Young Hee Lee通过一种直接快速瞬态测量方法,证明了二维单晶CuInP2S6(CIPS)薄片中清晰的纳秒负迁移态。此外,将这种超快的NC迁移与狄拉克接触的局域态密度和CIPS/通道(MoS2/石墨烯)中的受控电荷转移相结合,制备了一种最先进的器件结构—-负电容狄拉克源漏场效应晶体管(NCDSD-FET)。通过同时改善单层MoS2 FET中的传输因子和体因子,该器件具有50年内≈10mV/dec的平均SS,最低SS为4.8mV/dec,开关比超过107,优于先前所有报道。该研究为实现未来高速低功耗电子器件的超低SS FET铺平了道路。

相关研究工作以“Ultrafast Negative Capacitance Transition for 2d Ferroelectric MoS2/graphene Transistor”为题发表在国际顶级期刊《Advanced Materials》上。

三、研究内容

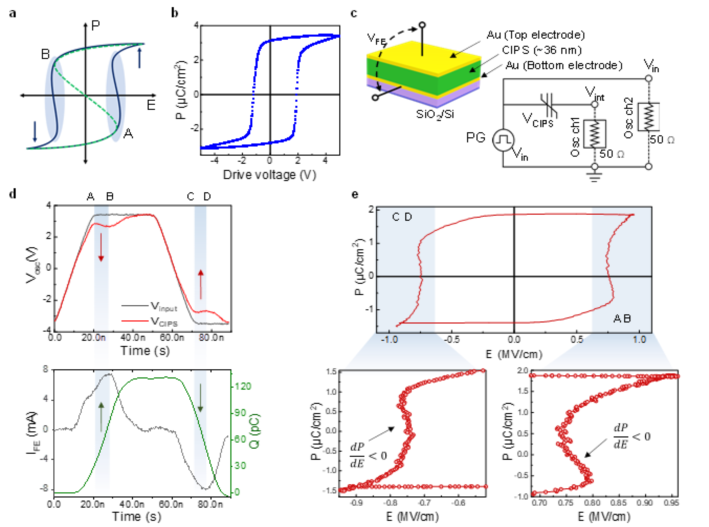

1、vdWs铁电体的负电容测量

如图1a所示,极化(P)相对于外加电场(E)的相应变化遵循理想的“S”形曲线。事实上,铁电电容器两端出现了额外的电阻压降,导致磁滞P-E行为,A和B区域周围保持负斜率。图1b显示了CIPS平行板电容器中典型的P-V磁滞回路,表明与HZO相比,极化开关尖锐。为了研究NC迁移性能,制作了Au/CIPS/Au金属铁电金属(MFM)结构(图1C),其CIPS厚度约为36nm,单元面积约为40×102μm2(D1)。图1d显示,测量电压(VCIPS)与输入电压(Vinput)的明显偏差具有负斜率,并且沿A-B区域有相关的电荷积累,表明差分电容存在负迁移,与典型的电容行为不同。区域A-B和C-D的放大图(图1e)显示了,CIPS中NC迁移的负斜率(dP/dE<0)。

图1. vdW铁电体CuInP2S6负电容的直接测量

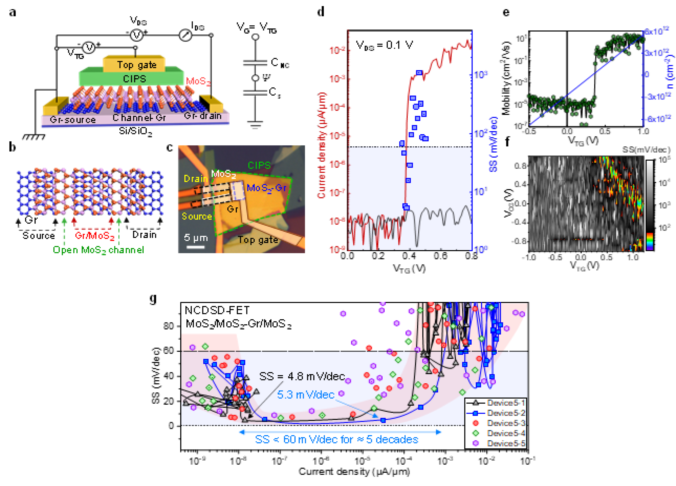

2、负电容和狄拉克源的混合

研究了五组器件结构,以确定性能最佳的超低SS FET(图2)。这包括:i)器件1:具有半金属双触点的MoS2-FET(图2a),ii)器件2:具有传统金属触点的MoS2-FET的铁电栅极绝缘体(图2b),iii)器件3:传统狄拉克源MoS2-FET(图2c),iv)器件4:具有狄拉克源触点的NC-FFET(图2d),v)器件5:具有MoS2和MoS2/Gr异质结构通道的负电容狄拉克源漏FET(图2e)。

在NC-FET结构(图2b)中,栅极电介质被铁电绝缘体取代,使得总体SS变得小于传输因子限制的SS。同时,DS-FET(图2c)利用Gr源的电荷中性点(CNP)周围的极局部化DOS来抵消热尾,前提是势垒高度低于狄拉克点(EDirac)的能量。在NCDS-FET(图2d)中,SBF和STF都减小了,因此SS预计将远低于玻尔兹曼极限值。图2e代表了本研究中最先进的器件结构。

图2.亚热离子SS的不同实现方法

3、NCDSD-FET的超低阈值摆幅

图3a说明了NCDSD-FET的示意性器件结构和等效电路图(器件5)。中间MoS2-Gr由浮动单层石墨烯组成,以促进高FET导通电流,而MoS2/MoS2-Gr/MoS2异质结构中单层MoS2的两个区域确保低FET关断电流。此外,使用两个单层石墨烯作为无间隙狄拉克接触(对于源极和漏极),以利用冷电子注入和随后的热尾抑制(图3b)。此外,铁电CIPS被用作玛瑙绝缘体(图3c),以在极低的工作电压内提供NC效应。器件5-1的传输(图3d)显示了典型的n型行为,开/关比达到~107。在VTG范围为-0.5到+1V时,器件5-1的双探针场效应迁移率(μFE)和载流子密度(n)如图3e所示。载流子密度n随VTG的增加而单调变化。同时,由于IDS的急剧变化,迁移率在阈值区域迅速升高,达到~21cm2/Vs的最高值。在VTG-VCG图中观察到亚热离子SS的明显存在,随着VCG从0增加到1 V,VTG从较高值~1.1 V到较低值0.4 V(图3f)。图3f显示,SS受到所应用的VC和VTG的强烈影响。表明随着VCG的增加,MoS2和Gr之间的肖特基势垒减小,以促进在较低VTG值下的超低SS。SS性能的再现性,可通过电流密度的函数来证明,如图3g所示。最好的器件5-2显示出4.8 mV/dec的创纪录的低SS,50年来平均SS为11mV/dec。5-1显示SSmin≈5.3mV/dec,50年的平均SS≈13mV/dec。所有五个设备的平均SS<10 mV/dec持续40多年。

图3. 50年来NCDSD-FET超低SS的演示

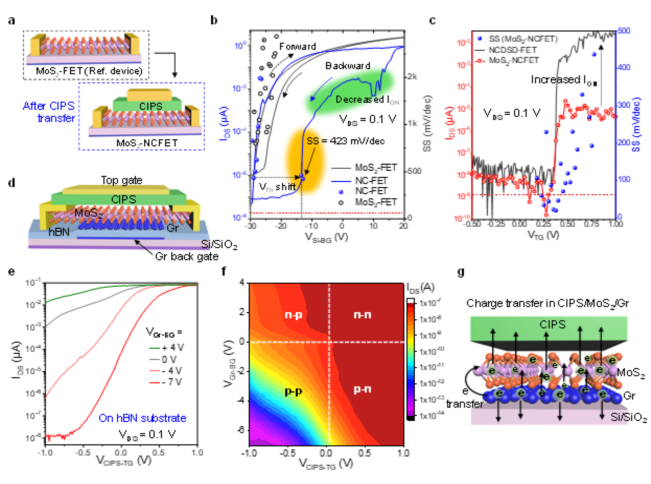

4、NCDSD-FET的工作原理

为了专门研究负电容的影响,构建了另一个具有CIPS层的NC-FET器件(图4a)。图4b显示,没有CIPS层的单层MoS2-FET表现出高导通电流(~4μA)、典型的磁滞和SSAvg(~700 mV/dec),远高于先前报道的热离子极限。具有CIPS层的NC-FET显示出VTh从-22.9V到13.8V的显著偏移,并且SS突然急剧下降。通过反向扫描,器件的导通电流减小,磁滞回线加宽~15V。表明电子从MoS2通道中提取。图4c中,NC-FET器件显示电流急剧上升,SS低至13.1mV/dec,VTh移动至0.45V。然而,导通电流明显限制在约10-5μA。在hBN衬底上,以MoS2/MoS2-Gr/MoS2为通道和两个局部栅极制作了一个双栅极NC-FET(图4d):i)CIPS顶栅极(CIPS-TG),以实现NC栅极绝缘体效应,ii)局部底部Gr栅极,以访问通道Gr的面板和区域。

图4e显示了在不同恒定背栅偏压(VGr-BG)下CIPS顶栅(IDS-VCIPS-TG)的传输特性。图4f绘制了VGr-BG和VCIPS-TG变化的IDS图。在n-n区,Gr和MoS2都是n型,平均电流水平为~10-7A,仍然受到源极和漏极附近开放MoS2区域的限制。在n-p和p-p区,MoS2是p型的,并且电流行为由Gr中的大多数载流子主导。这证明了,在n-p区,尽管顶部栅极有望关闭器件,但Gr的过量电子被注入到沟道中,从而保持高导通电流。如图4g所示,由于hBN衬底大大降低了可访问陷阱数量,Gr电子大多转移到MoS2。

图4. CuInP2S6对FET操作的影响

5、性能基准

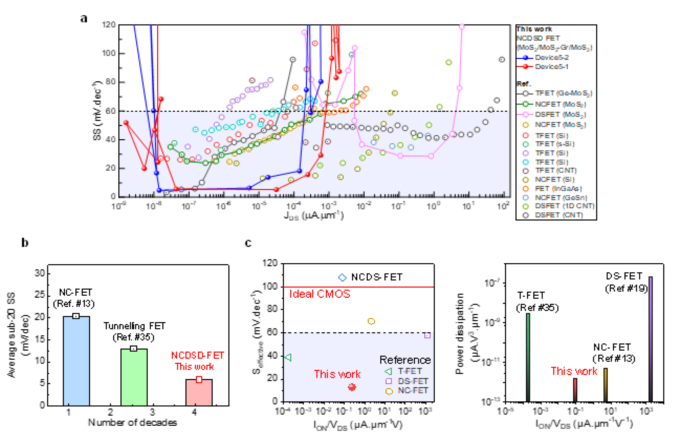

图5a显示,NCDSD-FET器件(器件5-1和器件5-2)在50年内的平均SS约为10mV/dec,最小SS值分别为5.3mV/dec(器件5-1)和4.8mV/dec(器件5-2)。明显优于之前报道的所有器件。NC-FET或DS-FET的性能无法与NCDSD-FET相媲美。图5b通过证明40年来平均SS值为6.1 mV/dec,超过了NC-FET、DS-FET和隧道FETs以前所有报道,从而推高了几十年内平均SS的下限。对于NCDSD-FET,S有效值仅为13mV/dec,高于TFET的~39mV/dec,远低于CMOS的值(图5c左)。有源模式下的功耗,是电源电压的三次指数(Pactive=IleakageVDS3)。NCDSD-FET的功耗,比文献中其他类型器件小得多(图5C右)。

图5. FET性能基准

四、结论与展望

总之,这项研究报道了使用铁电栅极绝缘体的狄拉克源漏FET,以突破60mV/dec的热力学极限。在FET中采用了NC概念(MFM电容器中观察到的),以直接证明平均SSavg的超低阈值摆幅。在50年内约为10mV/dec,最小值SSmin≈4.8mV/dec,这是文献中历史新低。尽管SS创下历史新低,但NCDSD-FET具有滞后的IDS-VGS特性,与CIPS中的亚稳态铁电操作相关。可以在CIPS和MoS2之间插入额外的氧化物层,使得CIPS电容(CNC)位于总MOS电容(CMOS)和氧化物电容(COX)之间,以实现无磁滞性能。通过混合改进的体因子和传输因子,在当前几十年内实现超低SS FET的策略,非常适用于下一代超低功率和高速电子器件。

文献链接:/10.1002/adma.202304338